- 亚博电竞菠菜

- 能源管理

- xinyabo体育

- 音频

- 传感器

- Lighting

- 自定义混合信号IC(ASIC)

- 电力转换

- 电源切换

- 记忆

- 硅IP.

- GreenPak可配置混合信号

- Timing

- 通讯

- IO-Link

- 工业和汽车ASIC

- 工业边缘计算

- IOX Expansion Module

- Izot调试工具(CT)

- Izot Net Server.

- Izot SDK 2

- IzoT ShortStack SDK

- LNS DDE服务器

- Lon升级

- Lonscanner FX协议分析仪

- Smart Edge Platform

- SmartServer IoT.

- SmartServer IoT.™ Partner Program

- SmartServer™IOT EDGE服务器

- U10 USB Network Interface

- U20 USB网络接口

- U60 DIN USB扩展模块

- U60 FT USB Network Interface Module

- U70 PL-20 USB网络接口

- 目前的控制

- 电机控制

- 显示

- 模块

- Longevity Program

- 产品选择器

- 文档搜索

- 亚博国际官网平台网址

- 支持

- 亚博全网

你在这里

发送预设数量的脉冲

发送预设数量的脉冲

Communication Protocols Technique

This technique can be done in any GreenPAK. Multi-function blocks within some GreenPAKs help reduce the component count.

In many communication protocols it’s necessary for a set number of bits to be sent or received by another IC. Typically, this means the GreenPAK must track the number of pulses sent or received. For example, in a shift register receiving data, the number of bits must be monitored to ensure that the expected data is in the correct register, rather than skewed incorrectly or unrelentingly continuing to shift.

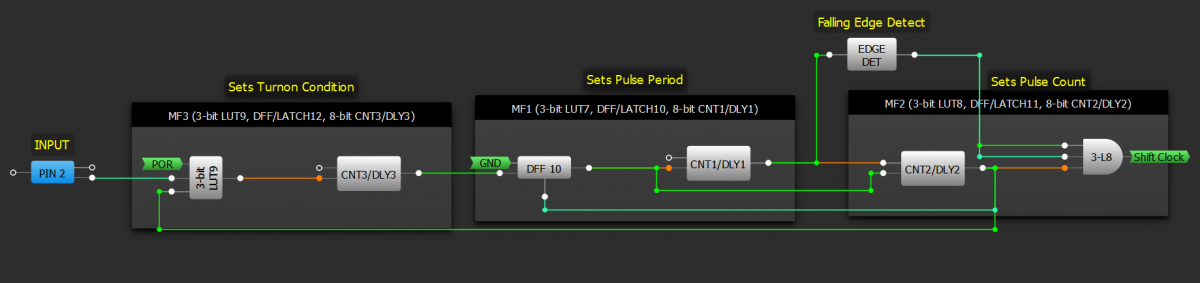

在GreenPak中设置预定数量的脉冲有很多方法:在该技术中描述了可扩展,有效的方式。它还通过重置每次交易后,通过重置时钟偏斜来限制在其他IC和GreenPak之间的时钟偏斜的增加的益处。图23示出了用于创建预设数量的脉冲的块的管道。它包括:Turnon条件,脉冲周期和脉冲计数器。

Figure 23 Preset Pulse Generator Design

该Turnon Condition stage has two components: a DLY block to ensure a minimum active signal to begin the pulse generation and a LUT to ensure the turnon condition isn’t re-instantiated before the last transaction has completed. Depending upon the application this stage may not be necessary.

该Pulse Period stage has two elements: a DFF and a counter. The DFF will disable theRESET_INsignal of the counter when the turnon condition is met. It will stay low until the pulse count has finished. The counter is used to set the period of the discrete pulses and can be configured to match the application.

该Pulse Count stage has a falling-edge delay and a logic gate. The delay’sCLK.连接到脉冲周期级的计数器,这导致它跟踪脉冲的数量。该dly延迟连接到脉冲周期级中的DFF。这导致延迟在设定的脉冲数后跌落,重置DFF并停止移位时钟。